Reduced instruction set computing para niños

En el mundo de las computadoras, RISC significa Reduced Instruction Set Computer, que en español se traduce como Computador con conjunto de instrucciones reducido. Es un tipo de diseño para la CPU (el "cerebro" de la computadora), que se usa mucho en microprocesadores y microcontroladores.

Las características principales de los diseños RISC son:

- Las instrucciones (las órdenes que la CPU entiende) tienen un tamaño fijo y se presentan de forma sencilla.

- Solo algunas instrucciones, las de "carga" y "almacenamiento", pueden acceder directamente a la memoria de datos.

Además, estos procesadores suelen tener muchos espacios de memoria muy rápidos llamados "registros", que usan para guardar información temporalmente.

El objetivo de crear computadoras con esta arquitectura es que puedan procesar las instrucciones de forma más eficiente, incluso varias a la vez (esto se llama segmentación y paralelismo), y que no necesiten acceder a la memoria principal tan seguido.

Hoy en día, muchos microprocesadores importantes usan el diseño RISC. Algunos ejemplos son PowerPC, DEC Alpha, MIPS, ARM y SPARC.

RISC es una forma de pensar cómo diseñar una CPU que prefiere instrucciones más pequeñas y sencillas. Estas instrucciones tardan menos tiempo en ejecutarse. Aunque los procesadores más comunes en las computadoras de escritorio, como los x86, se basan en un diseño diferente llamado CISC, las versiones más nuevas de estos procesadores a menudo convierten las instrucciones CISC en instrucciones más simples, parecidas a las RISC, para procesarlas internamente de forma más rápida.

La idea de RISC surgió porque se dieron cuenta de que muchas de las funciones complejas que se añadían a los diseños de CPU tradicionales no se usaban mucho en los programas. Además, la velocidad de los procesadores empezó a ser mucho mayor que la velocidad de la memoria a la que accedían. Esto llevó a buscar maneras de hacer que la CPU trabajara menos y accediera menos veces a la memoria.

Hoy en día, a estos diseños a veces se les llama "arquitecturas de carga-almacenamiento".

Contenido

¿Cómo se diseñaban las computadoras antes de RISC?

Un principio básico en el diseño de procesadores es incluir una memoria muy rápida para guardar información temporal. Estas memorias se llaman registros. Por ejemplo, para sumar dos números, la CPU primero los carga en los registros, los suma y guarda el resultado en otro registro. Luego, ese resultado se envía a la memoria principal.

Sin embargo, los registros son complejos de fabricar. Cada uno necesita muchos transistores en el chip, mientras que la memoria principal es más sencilla y económica. Además, los registros complican el cableado, porque la CPU necesita estar conectada a todos ellos para usarlos.

Por eso, muchos diseños de CPU antiguos limitaban el uso de registros. Algunos tenían pocos, lo que reducía su velocidad. Otros asignaban los registros a tareas específicas para simplificar el diseño.

En los años setenta, los procesadores eran lentos, a veces más lentos que la memoria. En esos casos, tenía sentido reducir los registros y dar a los programadores muchas formas de trabajar directamente con la memoria.

Volviendo al ejemplo de la suma, la mayoría de los diseños de CPU de esa época buscaban crear una sola instrucción que hiciera todo el trabajo: leer los dos números de la memoria, sumarlos y guardar el resultado directamente en la memoria. O leer uno de la memoria y otro de un registro, y guardar el resultado en la memoria. La meta era que cada instrucción pudiera hacer muchas cosas, un principio llamado ortogonalidad. Esto hacía la CPU muy compleja, pero en teoría, cada orden podía configurarse de muchas maneras.

Dos ejemplos famosos de este tipo de diseño son el MOS 6502 y el VAX. El chip 6502, que costaba unos 25 dólares, tenía solo un registro y, con un buen manejo de la memoria, podía ser más rápido que otros diseños más potentes. El VAX era una minicomputadora que, al principio, necesitaba tres armarios grandes solo para su CPU. Era conocido por la enorme variedad de formas en que podía acceder a la memoria y porque cada instrucción podía usar cualquiera de esas formas.

La idea detrás del diseño RISC

A finales de los años setenta, investigaciones en IBM y otros lugares mostraron que la mayoría de esas formas complejas de acceder a la memoria no se usaban en los programas. Esto se debía a que se empezaron a usar más los compiladores (programas que traducen el código que escriben los programadores a un lenguaje que la computadora entiende) en lugar de escribir directamente en lenguaje ensamblador (un lenguaje más cercano a las instrucciones de la máquina). Los compiladores solían ser más sencillos y no aprovechaban todas las características complejas de la CPU.

Otro descubrimiento importante fue que, como esas operaciones complejas se usaban poco, a menudo eran más lentas que hacer lo mismo con varias operaciones sencillas. Esto pasaba porque los diseñadores de CPU no tenían tiempo para optimizar cada instrucción posible, solo las más usadas. Por ejemplo, una instrucción compleja llamada `VAX INDEX` era más lenta que un conjunto de instrucciones más simples que hacían lo mismo.

Al mismo tiempo, las CPU empezaron a ser mucho más rápidas que la memoria. Se vio que esta diferencia seguiría creciendo, lo que significaba que las mejoras en las instrucciones complejas serían inútiles si la memoria era muy lenta.

Otra parte de la filosofía RISC vino de observar cómo funcionaban los programas en la vida real. Andrew Tanenbaum demostró que la mayoría de los procesadores eran "demasiado grandes" para lo que realmente se necesitaba. Por ejemplo, el 98% de los números constantes en un programa podían guardarse en 13 bits, pero los diseños de CPU siempre usaban múltiplos de 8 bits (8, 16 o 32 bits) para guardarlos. Esto sugería que se podían guardar constantes pequeñas en los espacios libres de otras instrucciones, reduciendo la necesidad de acceder a la memoria. En lugar de cargar números de la memoria, podían estar "ahí mismo" en la instrucción, haciendo el proceso mucho más rápido. Pero esto requería que las instrucciones fueran muy pequeñas.

El término "conjunto reducido de instrucciones" surgió por el pequeño número de modos y órdenes que se usaban. Sin embargo, esta no es una definición totalmente precisa, ya que los diseños RISC pueden tener muchas instrucciones. La verdadera diferencia es la idea de hacer todo con los registros y solo usar instrucciones de "carga" y "almacenamiento" para mover datos entre los registros y la memoria. Por eso, una forma más correcta de llamar a este diseño es "cargar-almacenar". Con el tiempo, los diseños antiguos se conocieron como "Computadora con Conjunto de Instrucciones Complejo", o CISC, solo para diferenciarlos.

Así, la filosofía RISC buscaba crear instrucciones pequeñas y simples. El código se construía con muchas de estas instrucciones sencillas, en lugar de una sola instrucción compleja. Esto dejaba más espacio dentro de la instrucción para llevar datos, lo que significaba que se necesitaban menos accesos a la memoria. Al mismo tiempo, la forma de interactuar con la memoria era más simple y se podía optimizar.

Sin embargo, RISC también tenía sus desventajas. Como se necesitan varias instrucciones para tareas sencillas, el número total de instrucciones que se leen de la memoria es mayor, y esto puede llevar más tiempo. Al principio, no estaba claro si RISC realmente mejoraría el rendimiento, y hubo muchos debates sobre los conceptos de RISC.

Multitarea en procesadores

En los procesadores RISC, es más fácil que la computadora realice varias tareas al mismo tiempo de verdad. Esto se debe a que sus instrucciones son más sencillas y uniformes. Los sistemas operativos diseñados para RISC pueden dividir el trabajo del procesador para que parezca que hay varios procesadores trabajando, reduciendo las instrucciones repetidas. Esto permite que los programas ejecuten varias tareas en un mismo ciclo de reloj. La memoria también se organiza de forma dinámica, asignando la cantidad necesaria a cada tarea.

En los procesadores CISC, la multitarea no es tan "real". Como tienen muchas instrucciones complejas y diferentes, no se pueden dividir tan fácilmente. La multitarea en CISC es más bien una "apariencia": el procesador atiende una tarea, luego otra, y así sucesivamente, dando la impresión de que trabajan al mismo tiempo. Esto se logra con técnicas como el "pipeline", que procesa diferentes etapas de varias instrucciones a la vez.

Los procesadores modernos son una mezcla de ambos. La parte que ve el usuario funciona como un CISC, pero las tareas que no están activas pueden traducirse a instrucciones RISC y procesarse de forma más eficiente. Las tareas que el usuario está usando activamente se manejan con el "pipeline" tradicional.

Una solución para la multitarea fue añadir un segundo procesador idéntico. Pero esto complicaba el manejo de la memoria y la compatibilidad con los módulos de memoria. También había problemas con la forma en que se organizaban los datos. Con el tiempo, estos problemas se hicieron más evidentes, especialmente con la llegada de las plataformas de 64 bits.

Historia de RISC

Mientras se desarrollaba la filosofía RISC, surgieron nuevas ideas para aumentar drásticamente el rendimiento de las CPU.

A principios de los años ochenta, se pensaba que los diseños de procesadores existentes estaban llegando a su límite. Se creía que las mejoras futuras vendrían de hacer los chips más pequeños. También se puso mucho esfuerzo en diseñar chips para la computación paralela, donde muchos chips trabajarían juntos para resolver un problema. Sin embargo, la historia demostró que estas preocupaciones no se hicieron realidad, y surgieron ideas que mejoraron mucho el rendimiento a finales de los ochenta.

Una de estas ideas fue el "pipeline" o Segmentación de cauce. Consiste en dividir el procesamiento de una instrucción en varios pasos. Un procesador normal lee una instrucción, la decodifica, la ejecuta y guarda el resultado. Con el "pipeline", el procesador puede empezar a leer la siguiente instrucción tan pronto como termina el primer paso de la anterior. Esto significa que varias instrucciones están en diferentes etapas de procesamiento al mismo tiempo. Aunque una sola instrucción no se completa más rápido, la siguiente instrucción se completa muy pronto, dando la sensación de un sistema mucho más veloz.

Otra solución fue usar varios elementos de procesamiento dentro del mismo procesador y ejecutarlos al mismo tiempo. Estos se llaman procesadores superescalares. En lugar de sumar dos números uno tras otro, un procesador superescalar podría ver la siguiente instrucción en el "pipeline" e intentar ejecutarla al mismo tiempo en otra unidad. Esto era complicado, ya que algunas instrucciones dependen del resultado de otras.

Ambas técnicas aumentaban la velocidad añadiendo complejidad al diseño de la CPU. Como el espacio en el chip es limitado, para incluir estas características, algo más tenía que eliminarse. RISC aprovechó estas técnicas porque su lógica interna era mucho más simple que la de los diseños CISC. Al principio, los diseños RISC ofrecían una mejora de rendimiento pequeña, pero pudieron añadir nuevas características y, a finales de los ochenta, superaron a sus contrapartes CISC. Con el tiempo, las mejoras en la fabricación de chips permitieron añadir estas características también a los diseños CISC, pero esto tardó casi una década.

Características de los procesadores RISC

En resumen, un chip RISC suele tener menos transistores dedicados a la lógica principal para un mismo nivel de rendimiento. Esto da a los diseñadores mucha flexibilidad. Por ejemplo, pueden:

- Aumentar el tamaño de los registros (esas memorias rápidas).

- Lograr una mayor velocidad al ejecutar las instrucciones.

- Implementar formas de aumentar el paralelismo interno (hacer varias cosas a la vez).

- Añadir memorias caché muy grandes (memorias intermedias muy rápidas).

- Añadir otras funciones, como entradas/salidas (E/S) y relojes para pequeños controladores.

- Fabricar los chips en líneas de producción más antiguas que de otra manera no se usarían.

- No añadir muchas funciones para que el chip consuma poca energía o sea muy pequeño.

Las características que suelen encontrarse en los diseños RISC son:

- Las instrucciones tienen un formato uniforme (por ejemplo, el código de operación siempre está en el mismo lugar), lo que permite decodificarlas más rápido.

- Los registros son homogéneos, lo que significa que cualquier registro se puede usar en cualquier situación, simplificando el trabajo de los compiladores.

- Los modos de acceso a la memoria son simples; los modos más complejos se reemplazan por varias instrucciones aritméticas sencillas.

- Los tipos de datos que el hardware soporta directamente (como cadenas de texto en algunas máquinas CISC) no suelen estar en una máquina RISC.

Muchos diseños RISC también usan un modelo de memoria Harvard, donde las instrucciones y los datos se guardan por separado. Esto significa que cambiar la dirección donde está el código no afecta las instrucciones que el procesador ejecuta (porque la CPU tiene cachés separados para instrucciones y datos). Además, permite acceder a ambos cachés al mismo tiempo, lo que puede mejorar el rendimiento.

Algunos de los primeros diseños RISC tenían una característica un poco complicada llamada "slot de salto retardado" (Delay Slot). Es un espacio para una instrucción justo después de un salto (cuando el programa cambia de una parte a otra). La instrucción en este espacio se ejecuta siempre, sin importar si el salto ocurre o no. Esto ayudaba a mantener la ALU de la CPU ocupada. Los compiladores tenían que organizar las instrucciones para que esto funcionara bien. Hoy en día, los diseños RISC modernos, como ARM, PowerPC y las versiones más recientes de SPARC y MIPS, generalmente han eliminado esta característica.

Primeros diseños RISC importantes

El primer sistema que hoy podríamos considerar RISC fue la supercomputadora CDC 6600, diseñada en 1964 por Seymour Cray.

Cray la diseñó para cálculos muy grandes. Tenía solo 74 códigos de instrucción (comparado con los 400 de un 8086) y 12 computadoras más simples para manejar las entradas y salidas.

El CDC 6600 usaba una arquitectura de carga/almacenamiento con solo dos formas de acceder a la memoria. Tenía once unidades funcionales para operaciones aritméticas y lógicas, además de cinco unidades para cargar datos y dos para almacenarlos. La memoria tenía varios bancos para que todas las unidades pudieran trabajar al mismo tiempo. En promedio, el procesador era 10 veces más rápido que el tiempo de acceso a la memoria.

Sin embargo, los diseños RISC más conocidos surgieron de proyectos de investigación universitarios financiados por el programa DARPA VLSI. Este programa, poco conocido hoy, llevó a grandes avances en el diseño y fabricación de chips.

Una de las primeras máquinas de carga/almacenamiento fue la minicomputadora Data General Nova, diseñada en 1968 por Edson de Castro. Tenía un conjunto de instrucciones casi puramente RISC, muy similar a los procesadores ARM actuales.

El proyecto RISC de la Universidad de Berkeley comenzó en 1980, dirigido por David A. Patterson. Se enfocaba en mejorar el rendimiento usando el "pipeline" y una técnica llamada "ventanas de registros". En una CPU normal, hay pocos registros que el programa puede usar en cualquier momento. En una CPU con ventanas de registros, hay muchos registros (138 en el RISC-I), pero los programas solo pueden usar un pequeño grupo de ellos (32 en el RISC-I) a la vez.

Un programa que se limita a 32 registros por procedimiento puede hacer llamadas a otros procedimientos muy rápido: al llamar o regresar, simplemente se mueve la "ventana" de 32 registros para dejar espacio de trabajo a la nueva parte del programa.

El proyecto RISC lanzó el procesador RISC-I en 1982. Tenía solo 44.420 transistores (comparado con los 100.000 de un diseño CISC de la época) y solo 32 instrucciones, pero aun así superaba el rendimiento de cualquier otro chip sencillo. El RISC-II, en 1983, tenía 40.760 transistores y 39 instrucciones, y era 3 veces más rápido que el RISC-I.

Casi al mismo tiempo, John Hennessy inició un proyecto similar llamado MIPS en la Universidad de Stanford en 1981. MIPS se centró en el "pipeline", asegurándose de que funcionara lo más "lleno" posible. Aunque el "pipeline" ya se usaba, varias características del chip MIPS lo hacían mucho más rápido. Lo más importante era que todas las instrucciones debían completarse en un solo ciclo. Esto permitía que el "pipeline" funcionara a velocidades muy altas, pero también eliminaba muchas instrucciones complejas, como la multiplicación o la división.

El primer intento de crear una CPU basada en el concepto RISC fue en IBM, que comenzó en 1975, antes de los proyectos de Berkeley y Stanford. Este trabajo llevó a la familia de procesadores IBM 801, muy usada en los equipos de IBM. El 801 se produjo como un chip llamado ROMP en 1981. Este chip fue diseñado para "tareas pequeñas", y cuando IBM lanzó un equipo basado en él, el IBM RT-PC en 1986, su rendimiento no fue el esperado. A pesar de esto, el 801 inspiró otros proyectos de investigación en IBM que llevaron a su sistema IBM POWER.

Al principio, todos los esfuerzos RISC eran conocidos, pero se limitaban a los laboratorios universitarios. Muchos en la industria criticaban que los beneficios de rendimiento no se traducirían en resultados reales. Pero a principios de 1986, todos los proyectos de investigación RISC empezaron a lanzar productos. De hecho, casi todos los procesadores RISC modernos son copias directas del diseño RISC-II.

RISC en la actualidad

La investigación de Berkeley no se comercializó directamente, pero el diseño RISC-II fue usado por Sun Microsystems para desarrollar el SPARC, por Pyramid Technology para sus máquinas multiprocesador, y por muchas otras compañías años después. El uso de RISC en los chips de SUN demostró que los beneficios de RISC eran reales, y sus máquinas rápidamente superaron a la competencia en el mercado de las estaciones de trabajo.

John Hennessy dejó Stanford para comercializar el diseño MIPS, fundando la compañía MIPS Computer Systems Inc. Su primer diseño fue el chip MIPS-II, conocido como R2000. Los diseños MIPS se hicieron muy populares al ser incluidos en las consolas de juego Nintendo 64 y PlayStation. Hoy en día, son procesadores muy usados en aplicaciones de alto nivel por Silicon Graphics.

IBM aprendió del fracaso del RT-PC y continuó con el diseño del RS/6000 basado en su nueva arquitectura IBM POWER. Luego, adaptaron sus computadoras centrales S/370 a los chips basados en IBM POWER, y se sorprendieron al ver que incluso el conjunto de instrucciones muy complejo (que era parte del S/360 desde 1964) funcionaba mucho más rápido. El resultado fue la nueva serie System/390, que aún hoy se vende como zSeries. El diseño IBM POWER también se adaptó para crear el diseño PowerPC, que eliminó muchas instrucciones "solo de IBM" y se implementó en un solo chip. El PowerPC se usó en todas las computadoras Apple Macintosh hasta 2006, y ahora se usa en automóviles (algunos vehículos tienen más de 10), y las consolas de videojuegos más recientes (PlayStation 3, Wii y Xbox 360) están basadas en PowerPC.

Casi todos los demás fabricantes se unieron rápidamente. En el Reino Unido, surgieron el INMOS Trasputer, el Acorn Archimedes y la línea Advanced RISC Machine, que hoy tiene mucho éxito. Las compañías con diseños CISC también se sumaron. Intel lanzó el i860 y el i960 a finales de los ochenta, aunque no tuvieron mucho éxito. Motorola construyó un nuevo diseño, pero no se usó mucho y finalmente lo abandonó, uniéndose a IBM para producir el PowerPC. AMD lanzó su familia 29000, que se convirtió en el diseño RISC más popular a principios de los noventa.

Hoy en día, los microcontroladores y CPU RISC representan la gran mayoría de todos los procesadores usados. La técnica de diseño RISC ofrece mucha potencia incluso en tamaños pequeños, y esto ha dominado por completo el mercado de CPU integrados de bajo consumo de energía. Los CPU integrados son, con mucho, los procesadores más comunes: una familia con una o dos computadoras personales puede tener varias docenas de dispositivos con procesadores integrados. RISC dominó por completo el mercado de las estaciones de trabajo. Después del lanzamiento de la SUN SPARCstation, otros fabricantes se apresuraron a competir con sus propias soluciones basadas en RISC. Aunque entre 2006 y 2010, las estaciones de trabajo pasaron a la arquitectura x86-64 de Intel y AMD. Incluso el mundo de las computadoras centrales ahora se basa completamente en RISC.

Esto es sorprendente, considerando el dominio de Intel x86 y x86 64 en el mercado de las computadoras personales de escritorio (y ahora también en estaciones de trabajo), laptops y servidores de gama baja. Sin embargo, RISC pudo avanzar en velocidad de forma muy rápida y económica.

Los diseños RISC han llevado al éxito a muchas plataformas y arquitecturas, algunas de las más importantes son:

- La línea MIPS Technologies Inc., que se encontraba en la mayoría de las computadoras de Silicon Graphics hasta 2006, y estuvo en las consolas ya descatalogadas Nintendo 64, PlayStation y PlayStation 2. Actualmente se usa en la PlayStation Portable y algunos routers.

- La serie IBM POWER, usada principalmente por IBM en servidores y supercomputadoras.

- La versión PowerPC de Motorola e IBM (una versión de la serie IBM POWER) usada en los ordenadores AmigaOne, Apple Macintosh como el iMac, eMac, Power Mac y posteriores (hasta 2006). Actualmente se usa en muchos sistemas integrados en automóviles, routers, etc., así como en muchas consolas de videojuegos, como la PlayStation 3, Xbox 360 y Wii.

- El procesador SPARC y UltraSPARC de Sun Microsystems y Fujitsu, que se encuentra en sus últimos modelos de servidores (y hasta 2008 también en estaciones de trabajo).

- El PA-RISC y el HP/PA de Hewlett-Packard, ya no se fabrican.

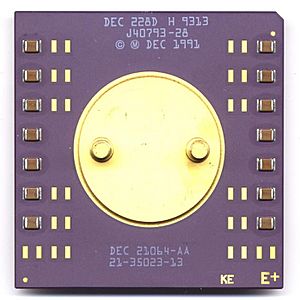

- El DEC Alpha en servidores HP AlphaServer y estaciones de trabajo AlphaStation, ya no se fabrican.

- El ARM – La capacidad de los procesadores ARM para convertir instrucciones x86 en operaciones RISC es muy importante para dispositivos móviles y pequeños, ya que ahorra espacio y energía. Por eso, los procesadores ARM dominan en PALM, Nintendo DS, Game Boy Advance y en muchas PDAs, Apple iPods, Apple iPhone, iPod Touch (Samsung ARM1176JZF, ARM Cortex-A8, Apple A4), Apple iPad (Apple A4 ARM -based SoC), videoconsolas como Nintendo DS (ARM7TDMI, ARM946E-S), Nintendo Game Boy Advance (ARM7TDMI).

- El Atmel AVR usado en una gran variedad de productos, desde controles de la Xbox hasta coches de la empresa BMW.

- La plataforma SuperH de Hitachi, usada originalmente para las consolas Sega Super 32X, Saturn y Dreamcast, ahora es el "corazón" de muchos equipos electrónicos de consumo. SuperH es la plataforma base del grupo Mitsubishi - Hitachi. Estos dos grupos, unidos en 2002, dejaron de lado la propia arquitectura RISC de Mitsubishi, el M32R.

- Los procesadores XAP usados en muchos chips inalámbricos de bajo consumo (Bluetooth, wifi) de CSR.

Galería de imágenes

-

Una consola del CDC 6600 mainframe system

Véase también

En inglés: Reduced instruction set computer Facts for Kids

En inglés: Reduced instruction set computer Facts for Kids

- Arquitectura de conjunto de instrucciones complejas

- Arquitectura computacional

- Arquitectura Harvard

- Arquitectura de von Neumann

- Modos de direccionamiento

- CISC

- Microprocesador

- Microcontrolador

- VLIW

- OpenRISC

- SISC