Arquitectura ARM para niños

Datos para niños Arquitectura ARM |

||

|---|---|---|

|

||

| Información | ||

| Tipo | Registro–Registro | |

| Desarrollador |

Sophie Wilson |

|

| Fecha de lanzamiento | 1985 | |

| Datos técnicos | ||

| Conjunto de instrucciones | RISC | |

| Ancho en bits | 32-bit • 64-bit | |

ARM, que antes significaba Advanced RISC Machine y originalmente Acorn RISC Machines, es un tipo de diseño de procesador. Imagina que es como el "cerebro" de muchos dispositivos electrónicos.

Estos procesadores usan una forma de trabajar llamada RISC (Reduced Instruction Set Computer), que significa "Ordenador con Conjunto Reducido de Instrucciones". Esto hace que sean más sencillos y eficientes.

Los procesadores ARM son muy populares. Se usan en la mayoría de los teléfonos móviles, tabletas, teléfonos inteligentes y relojes inteligentes que existen. También los encuentras en videoconsolas portátiles, calculadoras y otros aparatos.

Su diseño simple les permite usar menos energía y generar menos calor. Por eso son perfectos para dispositivos que funcionan con baterías.

Contenido

¿Qué es la Arquitectura ARM?

La arquitectura ARM es un conjunto de reglas que le dicen a un procesador cómo debe funcionar. Es como un plano o un manual de instrucciones para construir un cerebro electrónico.

Estos procesadores pueden manejar información en bloques de 32 o 64 bits. Esto se refiere a la cantidad de datos que pueden procesar al mismo tiempo.

¿Por qué ARM es tan popular?

Los procesadores ARM son muy eficientes. Necesitan menos componentes (transistores) que otros tipos de procesadores, como los que se usan en la mayoría de los ordenadores de escritorio.

Esta eficiencia significa que son más baratos de fabricar, consumen menos energía y no se calientan tanto. Estas características son ideales para dispositivos pequeños y portátiles.

Por ejemplo, en 2005, casi todos los teléfonos móviles vendidos usaban al menos un procesador ARM. Hoy en día, siguen siendo los más usados en la electrónica móvil.

¿Quién fabrica los procesadores ARM?

La empresa principal, ARM Holdings, no fabrica los chips directamente. En cambio, diseña los "planos" (llamados núcleos IP o propiedad intelectual) y vende licencias a otras empresas.

Esto significa que muchas compañías pueden fabricar sus propios procesadores basados en el diseño de ARM. Algunas de estas empresas son Apple Inc., Samsung, Qualcomm, Nvidia y Texas Instruments. Cada una puede añadir sus propias mejoras.

Historia de ARM

Los inicios en Acorn Computers

El diseño de ARM comenzó en 1983 en una empresa llamada Acorn Computers. Los ingenieros Sophie Wilson y Steve Furber lideraron el equipo.

Su objetivo era crear un procesador avanzado, pero que fuera fácil de usar para los programadores que ya conocían los ordenadores de Acorn.

Los primeros prototipos, llamados ARM1, estuvieron listos en 1985. La primera versión comercial, ARM2, se lanzó en 1986.

El ARM2 era muy simple para ser un procesador de 32 bits. Tenía pocos transistores, lo que lo hacía consumir poca energía y rendir bien.

La creación de Advanced RISC Machines

A finales de los años 80, Apple Computer empezó a colaborar con Acorn. Se dieron cuenta de que sería mejor si la empresa que diseñaba los procesadores no fuera también una empresa de ordenadores.

Así, en 1990, se creó una nueva compañía: Advanced RISC Machines (que luego se acortaría a ARM Holdings). Su misión era diseñar y gestionar las nuevas generaciones de procesadores ARM.

El trabajo llevó al ARM6 en 1991. Apple lo usó en su dispositivo Apple Newton.

El éxito en dispositivos móviles

La tecnología ARM se hizo muy popular con el procesador ARM7TDMI. Millones de estos chips se usaron en teléfonos móviles y consolas de videojuegos portátiles.

Otras grandes empresas como Digital Equipment Corporation (con su StrongARM) e Intel también licenciaron y desarrollaron procesadores basados en ARM.

Hoy en día, la mayoría de los procesadores de 32 bits en el mundo usan el diseño de ARM.

¿Cómo funciona un procesador ARM?

Los procesadores ARM tienen un conjunto de instrucciones que les permite realizar tareas de manera eficiente. Una característica interesante es que pueden decidir si ejecutar una instrucción basándose en una condición.

Por ejemplo, si el procesador necesita comparar dos números y luego hacer algo solo si uno es mayor que el otro, puede hacerlo de forma muy rápida. Esto ayuda a que el código sea más corto y el procesador trabaje más rápido.

También pueden combinar varias operaciones en una sola instrucción. Esto reduce la cantidad de veces que el procesador necesita acceder a la memoria, lo que mejora su rendimiento.

Modos de funcionamiento

Los procesadores ARM tienen dos modos principales:

- Modo ARM: Usa instrucciones de 4 bytes. Es más rápido y potente, pero consume más memoria y energía.

- Modo THUMB: Usa instrucciones de 2 bytes. Es más limitado, pero consume menos energía y es útil cuando el espacio de memoria es reducido.

Registros

Un procesador ARM tiene 16 "registros", que son como pequeños espacios de memoria dentro del procesador. Se usan para guardar datos temporalmente mientras el procesador trabaja. Tres de ellos tienen funciones especiales:

- R15: Es el contador de programa, que le dice al procesador dónde está en el código.

- R14: Guarda la dirección a la que debe volver el procesador después de terminar una tarea.

- R13: Se usa para manejar la memoria temporal (la "pila").

Tecnologías clave de ARM

Thumb

La tecnología Thumb es un conjunto de instrucciones más cortas (de 16 bits) que se añaden a las instrucciones estándar de ARM (de 32 bits).

Al usar instrucciones más cortas, se reduce el tamaño del código y se mejora la eficiencia, especialmente en dispositivos con memoria limitada. El primer procesador con Thumb fue el ARM7TDMI.

Jazelle

Jazelle es una tecnología que permite a los procesadores ARM ejecutar código Java de forma más directa y rápida. Esto es útil para aplicaciones que usan Java. Los procesadores con esta tecnología suelen tener una "J" en su nombre, como el ARM926EJ-S.

Sistemas Operativos que usan ARM

Los procesadores ARM son compatibles con muchos sistemas operativos, especialmente los que se usan en dispositivos móviles y sistemas integrados.

Sistemas para dispositivos móviles y embebidos

Muchos sistemas operativos populares funcionan con ARM, incluyendo:

- Android

- iOS (el sistema de los iPhone y iPad)

- Windows CE y Windows Embedded Compact

- Symbian

- FreeRTOS

- VxWorks

Sistemas tipo UNIX

Variantes de UNIX y sistemas basados en Linux también soportan ARM:

- Linux: Muchas distribuciones como Debian, Ubuntu, Arch Linux y Kali Linux funcionan en dispositivos ARM.

- BSD: Sistemas como FreeBSD, NetBSD y OpenBSD también son compatibles.

Windows

Microsoft ha adaptado su sistema operativo Windows para funcionar con procesadores ARM.

- Las versiones más recientes de Windows, como Windows 10 y Windows 11, tienen soporte para ARM. Esto permite que algunos ordenadores y tabletas con procesadores ARM puedan usar Windows.

- Windows Phone y Windows Mobile (sistemas operativos móviles de Microsoft) también usan ARM.

iOS y macOS

Apple ha usado procesadores ARM desde el lanzamiento del iPhone en 2007. Todos sus dispositivos móviles, como iPhone, Apple Watch, iPad y Apple TV, usan chips ARM.

Más recientemente, Apple ha empezado a usar procesadores ARM en todos sus ordenadores, como los iMac, MacBook, Mac Mini y Mac Pro. Esto se debe a que los chips ARM consumen menos energía y no necesitan tanta refrigeración, lo que los hace ideales para dispositivos más delgados y con mayor duración de batería.

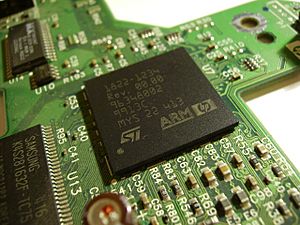

Galería de imágenes

-

Microprocesador ARM en un router.

Véase también

En inglés: ARM architecture family Facts for Kids

En inglés: ARM architecture family Facts for Kids