MIPS (procesador) para niños

MIPS es el nombre de una familia de microprocesadores. Un microprocesador es como el "cerebro" de un ordenador o de otros aparatos electrónicos. Los microprocesadores MIPS fueron creados por una empresa llamada MIPS Technologies. Son especiales porque usan una arquitectura llamada RISC, que significa que usan instrucciones más sencillas para trabajar más rápido.

Los diseños de MIPS se usan en muchos lugares. Por ejemplo, los encontrabas en las computadoras de SGI, en muchos sistemas electrónicos pequeños (como los que controlan electrodomésticos), en algunos dispositivos con Windows CE, en routers de Cisco y en videoconsolas muy populares como la Nintendo 64 y las Sony PlayStation, PlayStation 2 y PlayStation Portable. Incluso la NASA usó un procesador MIPS en la sonda espacial New Horizons para explorar el espacio.

Al principio, los procesadores MIPS trabajaban con 32 bits, lo que significa que podían manejar información en bloques de 32 "ceros" y "unos". Más tarde, se hicieron versiones de 64 bits, que son aún más potentes. Hay varias versiones de las instrucciones que MIPS puede entender, como MIPS I, MIPS II, MIPS III, MIPS IV y MIPS 32/64. También tienen "extensiones" que les permiten hacer tareas específicas, como gráficos 3D o manejar varias tareas al mismo tiempo.

Los procesadores MIPS son tan claros en su diseño que muchas universidades los usan para enseñar cómo funcionan los ordenadores. Su diseño también influyó en otros procesadores importantes, como los DEC Alpha.

Contenido

Historia de los Procesadores MIPS

¿Cómo Empezó MIPS?

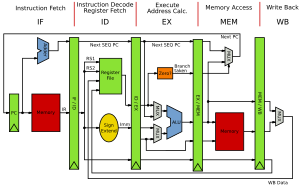

En 1981, un equipo de la Universidad de Stanford, liderado por John Hennessy, empezó a trabajar en el primer procesador MIPS. Su idea principal era hacer que los procesadores fueran mucho más rápidos usando una técnica llamada segmentación (o pipelining). Imagina que estás montando un coche: en lugar de esperar a que una persona termine de montar todo el coche, varias personas trabajan en diferentes partes al mismo tiempo. Así, el coche se monta más rápido.

En los procesadores, la segmentación divide el trabajo de una instrucción en varias etapas. Una etapa empieza antes de que la anterior haya terminado. Esto es diferente de los diseños antiguos, que esperaban a que una instrucción se completara del todo antes de empezar la siguiente. Con la segmentación, el procesador puede trabajar sin parar, lo que lo hace mucho más eficiente.

Un gran desafío de la segmentación era evitar que el procesador se "bloqueara" si una instrucción necesitaba esperar a otra. Los diseñadores de MIPS lograron que casi todas las etapas de las instrucciones se completaran en un solo ciclo de reloj. Esto eliminó la necesidad de bloqueos y permitió que los chips funcionaran a velocidades mucho más altas. Aunque esto significó que algunas operaciones complejas (como multiplicar o dividir) necesitaran varias instrucciones sencillas, el rendimiento general del sistema mejoró muchísimo.

De la Universidad a la Empresa

En 1984, John Hennessy vio el gran potencial de su diseño y dejó la universidad para fundar la empresa MIPS Computer Systems. En 1985, lanzaron su primer procesador, el R2000. Luego, en 1988, llegó el R3000. Estos procesadores de 32 bits fueron muy importantes en los años 80 y se usaron en estaciones de trabajo de SGI.

En 1991, MIPS lanzó su primer procesador de 64 bits, el R4000. Sin embargo, la empresa tuvo problemas económicos. Como el diseño era tan importante para SGI, que era uno de sus clientes principales, SGI compró MIPS Computer Systems en 1992. La empresa pasó a llamarse MIPS Technologies.

El Éxito de las Licencias

A principios de los años 90, MIPS empezó a permitir que otras empresas usaran sus diseños a cambio de una licencia. Esto fue un gran éxito porque los diseños de MIPS eran sencillos y eficientes. Muchas empresas los usaron en productos que antes usaban procesadores más complejos y menos potentes. A finales de los 90, los procesadores MIPS eran muy populares en los procesadores integrados (los que van dentro de otros aparatos). En 1997, se entregó el procesador MIPS número 48 millones, lo que demostró su gran éxito. Gracias a esto, SGI volvió a hacer de MIPS Technologies una empresa independiente en 1998. Hoy en día, gran parte de los ingresos de MIPS provienen de estas licencias.

En 1999, MIPS simplificó su sistema de licencias con dos diseños principales: el MIPS32 (de 32 bits) y el MIPS64 (de 64 bits). Empresas como NEC, Toshiba y Broadcom obtuvieron licencias. Los núcleos MIPS son muy usados en dispositivos como computadoras de mano, decodificadores de TV y sintonizadores. Incluso Freescale (una empresa de Motorola) usa procesadores MIPS en algunos de sus aparatos.

Familia de Procesadores MIPS

El primer procesador MIPS comercial, el R2000, salió en 1985. Podía hacer multiplicaciones y divisiones en una parte separada del procesador. Tenía 32 registros (pequeños espacios de memoria para guardar datos) de 32 bits. También podía trabajar con diferentes formas de organizar los datos (big-endian o little-endian).

El R3000 llegó en 1988, mejorando al R2000. Añadió una memoria caché (una memoria muy rápida para guardar datos que se usan a menudo) de 32 KB, que luego se amplió a 64 KB. También podía trabajar con varios procesadores al mismo tiempo. El R3000 fue el primer diseño MIPS que tuvo mucho éxito en el mercado, vendiendo más de un millón de unidades. Una versión más rápida, el R3000A, se usó en la famosa Sony PlayStation.

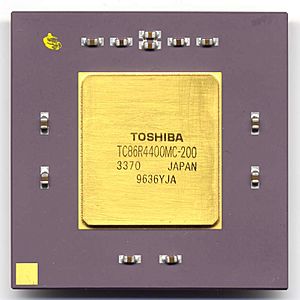

En 1991, el R4000 extendió las instrucciones de MIPS para trabajar con 64 bits y puso la unidad de punto flotante (para cálculos con números decimales) en el mismo chip. Funcionaba a una velocidad mucho mayor (100 MHz). Después del R4000, salieron muchas versiones mejoradas, como el R4400 en 1993, con cachés más grandes.

MIPS también diseñó versiones más económicas, como el R4200 y el R4300. La Nintendo 64 usa un procesador NEC VR4300, que se basa en el diseño de bajo costo R4300i de MIPS.

Otras empresas también crearon procesadores MIPS. Por ejemplo, Quantum Effect Devices (QED) diseñó el R4600 y el R5000, que eran conocidos por sus cachés grandes y eficientes. Estos se usaron en estaciones de trabajo SGI Indy y en routers Cisco. El R4650 se usó en los primeros aparatos de WebTV.

El R8000 (1994) fue el primer diseño MIPS que podía ejecutar varias operaciones al mismo tiempo (superescalar). Era muy potente para cálculos científicos, pero también muy caro.

En 1995, se lanzó el R10000. Este procesador era un solo chip, más rápido que el R8000 y con cachés más grandes. Su gran novedad fue que podía ejecutar instrucciones "fuera de orden", lo que significa que no tenía que seguir el orden exacto de las instrucciones si podía hacerlas más rápido de otra manera. Esto lo hizo muy popular.

Los diseños más recientes se basan en el R10000, como el R12000, R14000 y R16000. Estos tienen velocidades de reloj más altas, cachés más grandes y son más pequeños.

| Modelo | Frecuencia [MHz] | Año | Proceso [µm] | Transistores [millones] | Tamaño del chip [mm²] | Pines E/S | Potencia [W] | Voltaje | Caché de datos [k] | Caché de instrucciones [k] | Caché secundaria [k] |

|---|---|---|---|---|---|---|---|---|---|---|---|

| R2000 | 8-16,7 | 1985 | 2 | 0,11 | -- | -- | -- | -- | 32 | 64 | ninguna |

| R3000 | 12-40 | 1988 | 1,2 | 0,11 | 66,12 | 145 | 4 | -- | 64 | 64 | ninguna |

| R4000 | 100 | 1991 | 0,8 | 1,35 | 213 | 179 | 15 | 5 | 8 | 8 | 1024 |

| R4400 | 100-250 | 1992 | 0,6 | 2,3 | 186 | 179 | 15 | 5 | 16 | 16 | 1024 |

| R4600 | 100-133 | 1994 | 0,64 | 2,2 | 77 | 179 | 4,6 | 5 | 16 | 16 | 512 |

| R5000 | 150-200 | 1996 | 0,35 | 3,7 | 84 | 223 | 10 | 3,3 | 32 | 32 | 1024 |

| R8000 | 75-90 | 1994 | 0,5 | 2,6 | 299 | 591 | 30 | 3,3 | 16 | 16 | 1024 |

| R10000 | 150-250 | 1995 | 0,35 | 6,8 | 299 | 599 | 30 | 3,3 | 32 | 32 | 512 |

| R12000 | 270-400 | 1998 | 0,18–0,25 | 6,9 | 204 | 600 | 20 | 4 | 32 | 32 | 1024 |

| R14000 | 500-600 | 2001 | 0,13 | 7,2 | 204 | 527 | 17 | -- | 32 | 32 | 2048 |

| R16000 | 700-800 | 2002 | 0,11 | -- | -- | -- | 20 | -- | 64 | 64 | 4096 |

Nota: Estas especificaciones son de las configuraciones más comunes. Hay otras variaciones.

¿Dónde se Usan los Procesadores MIPS?

Uso en Estaciones de Trabajo

Al principio, los procesadores MIPS se usaban en estaciones de trabajo (computadoras potentes para profesionales) de empresas como SGI, MIPS Computer Systems, Inc., Olivetti y NEC. Varios sistemas operativos (como el cerebro principal de la computadora) funcionaban con MIPS, incluyendo SGI IRIX, Microsoft Windows NT (aunque ya no lo soporta), Windows CE, Linux y UNIX.

Sin embargo, el uso de MIPS en estaciones de trabajo ha disminuido. SGI, por ejemplo, decidió usar procesadores de Intel en sus computadoras más nuevas.

Uso en Sistemas Integrados

A pesar de esto, los microprocesadores MIPS siguen siendo muy importantes en los sistemas integrados. Estos son sistemas electrónicos pequeños que realizan tareas específicas, como los que se encuentran en routers, impresoras o decodificadores de TV. Los procesadores MIPS son ideales para esto porque consumen poca energía y son fáciles de usar para los desarrolladores.

Otros Modelos y el Futuro de MIPS

Otro miembro de la familia MIPS fue el R6000, que introdujo un nuevo conjunto de instrucciones (MIPS II). Sin embargo, no tuvo el éxito esperado. El PMC-Sierra RM7000 fue una versión del R5000 con una caché de nivel 2 integrada, diseñada para sistemas integrados y soluciones de red de Cisco.

SGI intentó en un momento cambiar de MIPS a los procesadores Intel Itanium, pero debido a retrasos, los procesadores MIPS siguieron siendo importantes. Por eso, se lanzaron versiones mejoradas como el R14000 y el R16000. Aunque SGI consideró hacer procesadores MIPS de doble núcleo, problemas financieros y el uso de otras tecnologías hicieron que el desarrollo de hardware IRIX/MIPS se detuviera.

Loongson

Loongson es una familia de microprocesadores diseñada en China por la Academia China de Ciencias. Aunque su diseño interno es propio, al principio les faltaban algunas instrucciones patentadas por MIPS Technologies. Sin embargo, en 2009, obtuvieron licencias de MIPS32 y MIPS64 directamente de MIPS Technologies.

Desde 2006, varias empresas han usado los procesadores Loongson en productos como computadoras de escritorio pequeñas y laptops de bajo consumo.

Núcleos MIPS

Hoy en día, gran parte de la tecnología MIPS se ofrece como "IP-cores" (bloques de construcción) para sistemas integrados. Esto significa que otras empresas pueden comprar la licencia para usar los diseños básicos de MIPS (conocidos como 4K para 32 bits y 5K para 64 bits) y combinarlos con otras unidades, como las que manejan cálculos decimales o entrada/salida.

Los núcleos MIPS son muy exitosos en la industria y en productos de consumo. Se encuentran en muchos routers modernos de Cisco, TP-Link y Linksys, en módems de cable y ADSL, tarjetas inteligentes, controladoras de impresoras láser, decodificadores de TV, robots, computadoras de mano, y en las consolas Sony PlayStation 2 y Sony PlayStation Portable.

Sin embargo, en el mundo de los teléfonos móviles y las PDAs, los núcleos MIPS no lograron superar a su competidor, la arquitectura ARM.

Programación y Emulación de MIPS

Para aprender a programar con MIPS, existen varios simuladores que permiten a los estudiantes practicar sin necesidad de tener un procesador MIPS real.

- SPIM es un simulador gratuito de MIPS R2000/R3000. Es muy útil para aprender a programar en lenguaje ensamblador MIPS y entender cómo funcionan los procesadores RISC. Puedes encontrarlo en [1].

- MARS (MIPS Assembler and Runtime Simulator) es otro simulador popular. Es un entorno de desarrollo fácil de usar, escrito en Java, que ayuda a programar MIPS en lenguaje ensamblador.

- GXemul (antes conocido como Proyecto mips64emul) es un emulador más completo. No solo simula diferentes versiones de procesadores MIPS (desde el R4000 hasta el R10000), sino también sistemas completos que usan esos procesadores. Por ejemplo, puede simular una DECstation o una SGI O2.

- El software QEMU también puede emular la arquitectura MIPS, permitiendo ejecutar sistemas operativos como GNU/Linux en una máquina simulada.

- Los simuladores CREATOR y WepSIM son herramientas educativas que se pueden usar para aprender a programar en MIPS y entender cómo funciona una CPU. WepSIM incluso se puede usar desde un navegador web.

Resumen de Llamadas al Sistema

Una "llamada al sistema" es cuando un programa le pide un servicio al sistema operativo. Por ejemplo, para mostrar algo en la pantalla o leer lo que escribes en el teclado.

Antes de pedir el servicio, el programa debe indicar qué servicio quiere usando un código especial en un "registro" (un espacio de memoria temporal en el procesador) llamado $v0. También debe poner la información necesaria en otros registros.

Aquí tienes algunos ejemplos de servicios comunes que se usan en simuladores como SPIM, MARS, CREATOR o WepSIM:

| Servicio | Código | Entrada | Salida | Notas |

|---|---|---|---|---|

| print_int | $v0=1 | $a0= número entero a imprimir | Imprime el número en la pantalla | |

| print_float | $v0=2 | $f12= número decimal a imprimir | Imprime el número decimal en la pantalla | |

| print_double | $v0=3 | $f12= número decimal grande a imprimir | Imprime el número decimal grande en la pantalla | |

| print_string | $v0=4 | $a0= dirección del primer carácter | Imprime un texto en la pantalla | |

| read_int | $v0=5 | Lee un número entero del teclado y lo guarda en $v0 | ||

| read_float | $v0=6 | Lee un número decimal del teclado y lo guarda en $v0 | ||

| read_double | $v0=7 | Lee un número decimal grande del teclado y lo guarda en $v0 | ||

| read_string | $v0=8 | $a0 = dirección del espacio, $a1= tamaño del espacio | Lee un texto del teclado y lo guarda en un espacio de memoria | |

| sbrk | $v0=9 | $a0= cantidad de bytes necesarios | Deja en $v0 la dirección de memoria reservada | Reserva espacio en la memoria |

| exit | $v0=10 | Termina el programa |

Resumen de las Instrucciones del R3000

Las instrucciones en MIPS se dividen en tres tipos: R, I y J. Todas las instrucciones comienzan con un "código de operación" de 6 bits, que le dice al procesador qué tipo de acción debe realizar.

- Las instrucciones tipo R (Registro) se usan para operaciones entre registros.

- Las instrucciones tipo I (Inmediato) se usan para operaciones que incluyen un valor constante.

- Las instrucciones tipo J (Salto) se usan para cambiar el flujo del programa, saltando a una nueva parte del código.

Registros del R3000

Los registros son como pequeñas cajas de almacenamiento dentro del procesador donde se guardan los datos que se están usando en ese momento. Cada registro tiene un nombre y un número. Algunos registros se "preservan" (su valor no cambia) cuando se llama a una subrutina (una parte del código que hace una tarea específica), y otros no.

| Nombre | Número | Uso | ¿Se guarda en subrutina llamada? |

|---|---|---|---|

| $zero | $0 | Siempre es 0 | sí |

| $at | $1 | Temporal para el ensamblador | no |

| $v0–$v1 | $2–$3 | Valores que devuelven las funciones | no |

| $a0–$a3 | $4–$7 | Argumentos que se pasan a las subrutinas | no |

| $t0–$t7 | $8–$15 | Temporales (no se guardan) | no |

| $s0–$s7 | $16–$23 | Temporales (se guardan) | sí |

| $t8–$t9 | $24–$25 | Temporales | no |

| $k0–$k1 | $26–$27 | Reservados para el sistema operativo | no |

| $gp | $28 | Puntero global | sí |

| $sp | $29 | Puntero de pila (para organizar la memoria) | sí |

| $fp | $30 | Puntero de marco de pila | sí |

| $ra | $31 | Dirección de retorno (a dónde volver después de una función) | no |

Instrucciones Básicas

Aquí hay algunos ejemplos de instrucciones que el procesador MIPS puede ejecutar directamente:

| Categoría | Nombre | Ejemplo de Uso | Qué Hace |

|---|---|---|---|

| Aritméticas | Suma | add $1,$2,$3 | $1 = $2 + $3 (suma dos registros) |

| Resta | sub $1,$2,$3 | $1 = $2 - $3 (resta dos registros) | |

| Suma inmediata | addi $1,$2,CONST | $1 = $2 + CONST (suma un número constante) | |

| Multiplicación | mult $1,$2 | Multiplica dos registros y guarda el resultado en registros especiales (HI y LO). | |

| División | div $1, $2 | Divide dos registros y guarda el resultado entero en LO y el resto en HI. | |

| Transferencia de datos | Carga de dirección | la $1, Etiqueta | $1 = Dirección de memoria de una etiqueta. |

| Carga de palabra | lw $1,CONST($2) | $1 = Carga un bloque de 4 bytes de la memoria. | |

| Carga de byte | lb $1,CONST($2) | $1 = Carga 1 byte de la memoria. | |

| Almacenamiento de palabra | sw $1,CONST($2) | Guarda un bloque de 4 bytes en la memoria. | |

| Almacenamiento de byte | sb $1,CONST($2) | Guarda 1 byte en la memoria. | |

| Carga del inmediato superior | lui $1,CONST | Carga un número constante en la parte superior de un registro. | |

| Mover desde "low" | mflo $1 | Mueve el valor del registro LO (resultado de división/multiplicación) a un registro normal. | |

| Lógicas | And | and $1,$2,$3 | $1 = $2 Y $3 (operación lógica bit a bit) |

| Or | or $1,$2,$3 | $1 = $2 O $3 (operación lógica bit a bit) | |

| Or exclusivo | xor $1,$2,$3 | $1 = $2 XOR $3 (operación lógica bit a bit) | |

| Nor | nor $1,$2,$3 | $1 = NO ($2 O $3) (operación lógica bit a bit) | |

| Inicializar si menor que | slt $1,$2,$3 | $1 = 1 si $2 es menor que $3, si no 0. | |

| Inicializar si menor que con inmediato | slti $1,$2,CONST | $1 = 1 si $2 es menor que CONST, si no 0. | |

| Desplazamiento de bits | Desplazamiento lógico a la izquierda | sll $1,$2,CONST | $1 = $2 movido CONST bits a la izquierda (multiplica por potencias de 2). |

| Desplazamiento lógico a la derecha | srl $1,$2,CONST | $1 = $2 movido CONST bits a la derecha (divide por potencias de 2, rellenando con ceros). | |

| Desplazamiento aritmético a la derecha | sra $1,$2,CONST | $1 = $2 movido CONST bits a la derecha (divide por potencias de 2, manteniendo el signo). | |

| Saltos condicionales | Salto si igual | beq $1,$2,CONST | Si $1 es igual a $2, salta a la dirección indicada. |

| Salto si no igual | bne $1,$2,CONST | Si $1 no es igual a $2, salta a la dirección indicada. | |

| Salto incondicional | Salto | j CONST | Salta siempre a la dirección indicada. |

| Salto a registro | jr $1 | Salta a la dirección guardada en el registro $1. | |

| Salto y enlace | jal CONST | Guarda la dirección de retorno en $31 y salta a la dirección indicada (para llamar a funciones). |

NOTA: En las instrucciones de saltos, CONST puede ser una "etiqueta" (un nombre para una parte del código).

Las "pseudoinstrucciones" son instrucciones que parecen una sola, pero el ensamblador (el programa que convierte el código en lenguaje de máquina) las traduce a varias instrucciones básicas antes de que el procesador las ejecute.

| Nombre | Ejemplo de Uso | Qué Hace |

|---|---|---|

| Saltar si mayor que | bgt $rs,$rt,Label | Si el valor de $rs es mayor que el de $rt, salta a la "Label". |

| Saltar si menor que | blt $rs,$rt,Label | Si el valor de $rs es menor que el de $rt, salta a la "Label". |

| Saltar si mayor o igual que | bge $rs,$rt,Label | Si el valor de $rs es mayor o igual que el de $rt, salta a la "Label". |

| Saltar si menor o igual que | ble $rs,$rt,Label | Si el valor de $rs es menor o igual que el de $rt, salta a la "Label". |

| Saltar si igual a cero | beqz $rs,Label | Si el valor de $rs es cero, salta a la "Label". |

Galería de imágenes

-

Un microprocesador MIPS R4400 fabricado por Toshiba.

Véase también

En inglés: MIPS architecture Facts for Kids

En inglés: MIPS architecture Facts for Kids