Intel Itanium para niños

Datos para niños Intel Itanium |

||

|---|---|---|

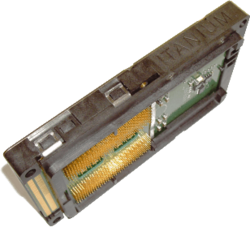

Procesador Itanium

|

||

| Información | ||

| Tipo | marca | |

| Desarrollador | Intel | |

| Fabricante |

|

|

| Fecha de lanzamiento | Junio de 2001 | |

| Descontinuación | Actualidad | |

| Datos técnicos | ||

| Frecuencia de reloj de CPU | 733MHz — 1.73GHz | |

| Velocidad de FSB | 300MHz — 667MHz | |

| Conjunto de instrucciones | Itanium | |

| Número de núcleos | 1, 2 o 4 | |

| Núcleos | ||

|

||

| Se conecta a | ||

| Zócalo(s) |

|

|

El Itanium, también conocido por su nombre clave Merced, fue un tipo de microprocesador creado por Intel. Fue el primero en usar una arquitectura especial llamada Arquitectura Intel Itanium, que fue diseñada por Hewlett-Packard y desarrollada junto con Intel.

Aunque se esperaba que saliera en 1998, el Itanium no llegó al mercado hasta mayo de 2001. Este procesador se fabricaba con una tecnología de 180 nanómetros (un nanómetro es una medida muy, muy pequeña).

Contenido

¿Qué características tenía el procesador Intel Itanium?

El procesador Itanium tenía varias características técnicas importantes para su funcionamiento.

Memoria y velocidad

El Itanium incluía diferentes niveles de memoria caché, que es una memoria muy rápida que ayuda al procesador a trabajar más rápido. Tenía:

- 32 KB de caché de primer nivel (L1), dividida para datos e instrucciones.

- 96 KB de caché de segundo nivel (L2) dentro del procesador.

- 2 o 4 MB de caché de tercer nivel (L3) fuera del procesador principal.

Este procesador estaba disponible en versiones con velocidades de 733 u 800 MHz (megahercios).

¿Cómo funcionaba la arquitectura Itanium?

La forma en que el Itanium estaba diseñado era muy diferente a otros procesadores de Intel, como los x86. Su arquitectura se basaba en algo llamado "paralelismo explícito a nivel de instrucción".

Esto significa que el compilador (un programa que traduce el código de programación a un lenguaje que el procesador entiende) decidía qué instrucciones se podían ejecutar al mismo tiempo. Gracias a esto, el Itanium podía procesar hasta seis instrucciones en cada ciclo de reloj. A diferencia de otros procesadores, no necesitaba un hardware complicado para saber qué instrucciones dependían de otras.

¿Cuál fue el impacto del Itanium en el mercado?

Cuando se lanzó en junio de 2001, el Itanium no fue mejor que otros microprocesadores de la época. Competía con procesadores RISC y CISC en el mercado de servidores pequeños. También se enfrentaba a arquitecturas como IBM POWER y SPARC en el mercado de servidores más grandes.

Reposicionamiento y desafíos

Intel intentó que el Itanium se enfocara en computadoras de alto rendimiento (HPC), que son máquinas muy potentes usadas para cálculos complejos. Su éxito fue limitado, principalmente reemplazando sistemas antiguos de HP y Silicon Graphics.

Sin embargo, las arquitecturas POWER y SPARC siguieron siendo fuertes. Además, los procesadores x86, que eran más comunes, crecieron mucho en el mundo empresarial. Debido a esto, Intel y HP se dieron cuenta de que el Itanium no era tan competitivo como esperaban.

El reemplazo del Itanium

Por estas razones, el Itanium fue reemplazado por el Intel Itanium 2 un año antes de lo planeado, en 2002. Solo se vendieron unos pocos miles de unidades del Itanium original. Esto se debió a que no se produjeron muchas, su rendimiento no era el esperado y su costo era alto. A pesar de esto, las máquinas con Itanium fueron útiles para desarrollar programas para los futuros procesadores Itanium 2.

Galería de imágenes

Véase también

En inglés: Itanium Facts for Kids

En inglés: Itanium Facts for Kids

- Arquitectura Intel Itanium

- Intel Itanium 2