DRAM para niños

La memoria dinámica de acceso aleatorio o DRAM (del inglés dynamic random-access memory) es un tipo de memoria que usan los ordenadores y otros aparatos electrónicos. Es como un cuaderno donde el ordenador guarda información temporalmente mientras la está usando.

La DRAM funciona con pequeños componentes llamados condensadores. Estos condensadores guardan una pequeña carga eléctrica que representa un "1" o un "0" (los bits de información). El problema es que los condensadores pierden su carga poco a poco, como una pila que se descarga. Por eso, la DRAM necesita un circuito especial que está siempre "refrescando" o recargando esos condensadores para que la información no se pierda. Esto ocurre muy rápido, ¡millones de veces por segundo!

A diferencia de la DRAM, existe otro tipo de memoria llamada SRAM (RAM estática), que no necesita este refresco constante. Sin embargo, la DRAM es muy popular porque permite construir memorias con mucha capacidad y que funcionan a gran velocidad. Por eso, se usa principalmente como la memoria principal de los ordenadores.

Como todas las memorias RAM, la DRAM es "volátil". Esto significa que si el ordenador se apaga o se queda sin electricidad, toda la información que estaba guardada en la DRAM se pierde. Fue inventada a finales de los años sesenta y sigue siendo una de las memorias más usadas hoy en día.

Contenido

Historia de la Memoria DRAM

La memoria dinámica fue creada en los laboratorios de IBM. Al principio, las memorias usaban varios transistores, pero Robert Dennard logró un gran avance en 1968. Él inventó una memoria DRAM que usaba solo un transistor y un condensador por cada bit de información. Esto hizo que las memorias fueran mucho más pequeñas y eficientes.

En ese tiempo, IBM usaba principalmente memorias basadas en núcleos magnéticos. Aunque la nueva DRAM era más rápida, IBM no la vio como un producto para vender a otras empresas.

Fue la empresa Intel la que vio una gran oportunidad. En 1970, Intel lanzó el i1103, su primer producto de DRAM. Este chip podía guardar 1024 bits de información y era mucho más barato que las memorias de núcleo magnético. Aunque al principio tuvo algunos desafíos de producción, el i1103 se volvió muy popular. Para finales de 1971, ya era la memoria principal preferida por la mayoría de los fabricantes de ordenadores.

¿Cómo se hizo más eficiente la DRAM?

Al principio, los chips de DRAM necesitaban muchos "pines" (las patitas metálicas que se conectan a la placa del ordenador) para enviar y recibir la información. Cuantos más pines, más caro y complicado era fabricar el chip.

En 1973, Robert Proebsting encontró una solución inteligente. Se dio cuenta de que la información de la dirección de memoria (dónde está guardado un dato) podía enviarse en dos partes, una después de la otra. Esto se llama "direccionamiento multiplexado". Gracias a esto, se redujo mucho la cantidad de pines necesarios en los chips de DRAM. Por ejemplo, un chip que antes necesitaba 16 pines para las direcciones, ahora solo necesitaba 8. Esta idea fue tan buena que se convirtió en un estándar de la industria y todavía se usa en las memorias DRAM actuales.

¿Cómo funciona la Memoria DRAM?

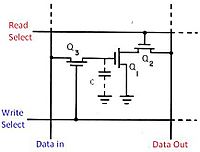

La unidad más pequeña de una memoria se llama "celda de memoria". En la DRAM moderna, cada celda está formada por un transistor y un condensador. El condensador guarda la carga eléctrica (un "1" o un "0"), y el transistor actúa como un interruptor que permite o no que la carga entre o salga del condensador.

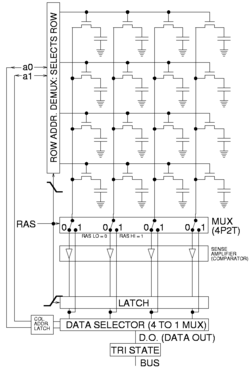

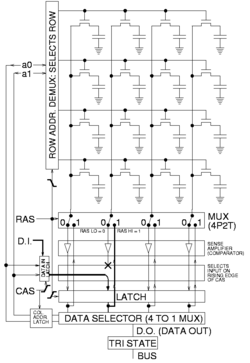

Las celdas de memoria se organizan en filas y columnas, como una cuadrícula gigante. Cuando el ordenador quiere leer o escribir un dato, envía una dirección que indica la fila y la columna donde se encuentra la celda deseada.

Para leer un dato, el proceso es así:

- Primero, las líneas de las columnas se preparan con un voltaje específico.

- Luego, se activa la fila donde está la celda que queremos leer. Esto hace que el transistor de esa celda se abra y conecte el condensador a la línea de la columna.

- La pequeña carga del condensador de la celda se mezcla con la carga de la línea de la columna. Aunque el cambio es muy pequeño, unos circuitos especiales llamados amplificadores lo detectan y lo "redondean" para saber si era un "1" o un "0".

- Finalmente, el dato se envía al ordenador. Es importante saber que al leer un dato de la DRAM, la carga del condensador se altera, por lo que la información debe ser "reescrita" inmediatamente después de ser leída para que no se pierda.

Para escribir un dato, el proceso es similar, pero en lugar de leer la carga, se envía una nueva carga a la línea de la columna, y esta carga se guarda en el condensador de la celda.

Diseño de las Celdas de Memoria

Cada bit de información en una DRAM se guarda como una carga eléctrica en un condensador. La parte que guarda la carga y los transistores que la controlan se llaman "celda DRAM". La celda más común en las DRAM modernas es la de un transistor y un condensador (1T1C). El transistor ayuda a que la corriente entre al condensador cuando se guarda un dato y a que salga cuando se lee.

El condensador tiene dos conexiones. Una se conecta al transistor y la otra a tierra o a la mitad del voltaje de la fuente de energía. En las DRAM actuales, se usa la mitad del voltaje para que funcione más rápido. Para guardar un "1", el condensador tiene un voltaje positivo; para un "0", tiene un voltaje negativo.

¿Cómo se diseñan los condensadores?

Hasta mediados de los años 80, los condensadores de las celdas DRAM se construían en la misma superficie que el transistor. Pero para hacer las memorias más pequeñas y con más capacidad, los ingenieros tuvieron que ser más creativos.

Así, los condensadores se empezaron a construir "apilados" (uno encima del otro) o "enterrados" (debajo de la superficie del chip). Esto permitió que las celdas de memoria ocuparan menos espacio, lo que significa que se pueden poner más celdas en un mismo chip y, por lo tanto, tener más memoria a un costo menor. Hoy en día, la mayoría de los grandes fabricantes de DRAM usan la estructura de condensadores apilados.

Galería de imágenes

Véase también

En inglés: Dynamic random-access memory Facts for Kids

En inglés: Dynamic random-access memory Facts for Kids

- SRAM

- A-RAM

- Tubo Williams

- FPM DRAM

el:Μνήμη τυχαίας προσπέλασης#Τύποι μνήμης RAM