SRAM para niños

SRAM son las siglas en inglés de Static Random Access Memory, que significa memoria estática de acceso aleatorio. Es un tipo de memoria de computadora que puede guardar datos mientras recibe energía, sin necesidad de un circuito especial para "refrescar" la información. Esto la diferencia de la memoria DRAM (RAM dinámica), que sí necesita refrescar sus datos constantemente.

Existen dos tipos principales de SRAM: las volátiles y las no volátiles. La diferencia es que las memorias volátiles pierden sus datos cuando se apaga la energía, mientras que las no volátiles los conservan.

Contenido

¿Cómo funciona la memoria SRAM?

Las memorias SRAM son de acceso aleatorio. Esto significa que puedes leer o escribir información en cualquier parte de la memoria en cualquier orden. No importa dónde hayas accedido antes.

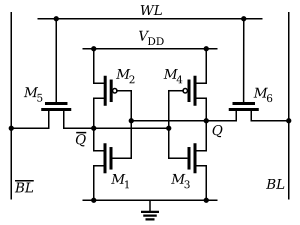

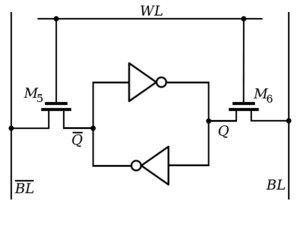

Cada pequeña pieza de información, llamada bit, se guarda en una celda de memoria SRAM. Esta celda suele usar seis componentes electrónicos llamados transistores. Cuatro de estos transistores forman un circuito especial llamado biestable, que tiene dos estados estables para guardar un 0 o un 1. Los otros dos transistores controlan cuándo se puede acceder a esa celda para leer o escribir datos.

Algunos tipos de SRAM pueden usar más transistores por bit, como ocho o diez. Esto se hace para funciones especiales, como en algunas memorias de video. Cuantos menos transistores se usen por celda, más pequeñas pueden ser las celdas. Esto ayuda a reducir el costo de fabricación, ya que se pueden poner más celdas en un mismo chip.

El acceso a cada celda de memoria se controla mediante un "bus de control" (llamado WL en los diagramas). Este bus activa los transistores que conectan la celda a los "buses de datos" (BL y BL). Estos buses de datos se usan para enviar y recibir información durante la lectura y escritura.

A diferencia de la memoria DRAM, que usa condensadores para guardar la información, las celdas SRAM usan los biestables para mantener la señal. Esto permite que la SRAM detecte cambios de voltaje con mayor precisión. Otra ventaja es que la SRAM puede recibir todas las direcciones de memoria al mismo tiempo, lo que la hace más rápida.

Modos de operación de una SRAM

Una memoria SRAM puede estar en tres estados diferentes:

- Reposo (Standby): Cuando no se está usando, el circuito está tranquilo.

- Lectura (Reading): Cuando se están leyendo datos de la memoria.

- Escritura (Writing): Cuando se están guardando o actualizando datos en la memoria.

Reposo

Cuando el bus de control (WL) no está activo, los transistores de acceso desconectan la celda de los buses de datos. Los biestables dentro de la celda mantienen la información guardada mientras la memoria siga recibiendo energía.

Lectura

Para leer, primero se preparan los buses de datos. Luego, se activa el bus de control (WL). La información guardada en la celda se transfiere a los buses de datos. Por ejemplo, si la celda guarda un 1, uno de los buses de datos se mantendrá igual y el otro cambiará a 0. Si la celda guarda un 0, ocurrirá lo contrario.

Escritura

Para escribir, se envía la información que se quiere guardar a los buses de datos. Luego, se activa el bus de control (WL) y la información se guarda en la celda de memoria.

¿Para qué se usa la memoria SRAM?

Características importantes

La memoria SRAM es más costosa que la DRAM, pero es más rápida y consume menos energía, especialmente cuando está en reposo. Por eso, se usa cuando se necesita que la información se acceda muy rápido o cuando el consumo de energía debe ser bajo.

Debido a su diseño más complejo, la SRAM no puede guardar tanta información en el mismo espacio como la DRAM. Por eso, no se usa como la memoria principal de las computadoras personales, donde se necesita mucha capacidad.

Consumo de energía

El consumo de energía de una SRAM cambia según la frecuencia con la que se usa. Si se usa muy rápido, puede consumir tanta energía como una DRAM. Pero si se usa a baja frecuencia, consume muy poca energía, lo que la hace ideal para dispositivos que funcionan con baterías.

Usos comunes de las SRAM

La SRAM se usa en muchos lugares:

- Como chips individuales: Se usan en equipos de comunicación, como los que controlan el internet en casa (routers) o los teléfonos por internet.

- Dentro de otros chips:

* Como memoria principal o memoria caché en pequeños cerebros electrónicos llamados microcontroladores. * Para guardar información temporalmente en los microprocesadores de las computadoras. * En otros circuitos electrónicos complejos. * En dispositivos programables como FPGAs y CPLDs.

En productos de uso diario

Puedes encontrar memoria SRAM en:

- Sistemas científicos e industriales.

- Electrónica de automóviles.

- Casi todos los productos electrónicos que tienen una pantalla o botones para que los uses.

- Computadoras personales, estaciones de trabajo y la mayoría de los dispositivos que se conectan a la computadora (periféricos).

Para aficionados a la electrónica

A quienes les gusta construir sus propios circuitos electrónicos, prefieren la SRAM. Es más fácil de usar que la DRAM porque no necesita "refrescarse" y se puede acceder directamente a sus conexiones. Además, la SRAM solo necesita unas pocas señales de control para funcionar.

Tipos de SRAM

SRAM no volátiles

Las SRAM no volátiles (NVRAM) son especiales porque guardan la información incluso si se les corta la energía. Son útiles cuando no se quiere usar baterías para mantener los datos.

SRAM asíncrona

Las SRAM asíncronas son rápidas y se usan en equipos de comunicación, como los que manejan las redes de internet, y en la electrónica de los coches.

Por tipo de transistor

- Transistor de unión bipolar (BJT): Son muy rápidos, pero consumen mucha energía.

- MOSFET (CMOS): Consumen menos energía y son los más usados hoy en día.

Por función

- Asíncronas: Funcionan sin depender de una señal de reloj.

- Síncronas: Todas sus operaciones son controladas por la señal de reloj del sistema.

Véase también

En inglés: Static RAM Facts for Kids

En inglés: Static RAM Facts for Kids