Caché (informática) para niños

En informática, una caché (también llamada antememoria o memoria intermedia) es como un pequeño almacén muy rápido que guarda copias de datos que tu computadora usa con frecuencia. Imagina que es un atajo: en lugar de ir hasta el almacén principal (la memoria más lenta) cada vez que necesitas algo, la caché lo tiene a mano para que lo uses al instante.

Cuando la computadora busca un dato y lo encuentra en la caché, se llama acierto de caché. Si no lo encuentra, es un fallo de caché y tiene que ir a buscarlo a la memoria principal, lo que toma más tiempo. Cuantos más aciertos tenga la caché, más rápido funcionará tu sistema.

La caché de memoria es una parte especial de la memoria de tu unidad central de procesamiento (CPU). Guarda temporalmente los datos que el procesador acaba de usar o que probablemente usará pronto. Es mucho más pequeña que la memoria principal (RAM), pero muchísimo más veloz. Su objetivo principal es ayudar al microprocesador a acceder a los datos más rápido, evitando que tenga que esperar por la memoria principal.

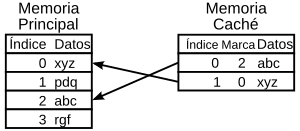

Cuando tu computadora necesita un dato, primero mira en la caché. Si está allí, lo toma de inmediato. Si no, lo busca en la memoria principal y, al encontrarlo, hace una copia en la caché para futuros usos.

De manera similar, existe la caché de software, como la que usan los navegadores de internet. Cuando visitas una página web, tu navegador guarda una copia de las imágenes y textos en tu disco duro. Así, la próxima vez que visites esa página, no tiene que descargar todo de nuevo de internet, lo que hace que la página cargue mucho más rápido.

Contenido

¿Por qué es Importante la Caché?

La caché es crucial porque ayuda a que tu computadora sea mucho más rápida. Hay dos razones principales para esto:

Menos Esperas: La Latencia

Imagina que tu procesador es un chef muy rápido, pero los ingredientes están en una despensa muy lejana. Cada vez que el chef necesita un ingrediente, tiene que ir hasta la despensa, lo que le hace perder tiempo. La caché es como tener una pequeña nevera justo al lado del chef con los ingredientes más usados. Así, el chef no tiene que esperar tanto. En informática, a esta espera se le llama latencia. La caché reduce esta espera, permitiendo que el procesador trabaje sin interrupciones.

Más Datos a la Vez: El Ancho de Banda

La caché también ayuda a mover más datos al mismo tiempo. Piensa en una tubería: si solo envías gotas de agua una por una, no aprovechas toda la capacidad de la tubería. Pero si envías grandes chorros de agua, la usas de manera más eficiente. La caché agrupa las pequeñas solicitudes de datos en paquetes más grandes, lo que permite que se transfieran más datos a la vez y se aproveche mejor la capacidad de la memoria principal.

Tipos de Caché en Computadoras

Existen diferentes tipos de caché, cada uno con una función específica para mejorar el rendimiento:

Caché de Disco

Esta caché usa una parte de la memoria RAM para guardar los datos que se han leído recientemente del disco duro. Acceder a la RAM es miles de veces más rápido que acceder al disco duro. Por eso, si un programa necesita los mismos datos otra vez, la caché de disco los tiene listos, acelerando mucho el trabajo de las aplicaciones.

Caché de Pista

Este tipo de caché es una memoria muy rápida y costosa, hecha de componentes electrónicos. Se usa principalmente en supercomputadoras, que son máquinas muy potentes que necesitan la máxima velocidad posible.

Caché Web

La caché web guarda copias de páginas web, imágenes y otros archivos que descargas de Internet. Esto ayuda a que las páginas carguen más rápido la próxima vez que las visites, reduce la cantidad de datos que tienes que descargar y disminuye la carga en los servidores de internet. Hay cachés web privadas (para un solo usuario) y compartidas (para varios usuarios).

Niveles de Caché en el Procesador

Dentro del microprocesador, la caché se organiza en diferentes niveles, como si fueran pisos de un edificio, cada uno con su propia velocidad y tamaño:

Caché L1: La Más Rápida

Esta es la caché más cercana al corazón del procesador. Es la más pequeña, pero también la más rápida. Se divide en dos partes: una para guardar los datos que el procesador usa (Data Cache) y otra para guardar las instrucciones que le dicen al procesador qué hacer (Instruction Cache).

Caché L2: Un Poco Más Grande

La caché L2 es más grande que la L1, pero un poco más lenta. Aun así, es mucho más rápida que la memoria principal (RAM). Guarda datos que se usan con frecuencia y puede contener una copia de lo que hay en la L1 o información diferente para aumentar la capacidad total.

Caché L3: Para Más Información

La caché L3 es la más grande de las cachés del procesador, pero también la más lenta de las tres. Su función es guardar una gran cantidad de información para que el procesador no tenga que ir a la RAM tan a menudo. Si un dato no se encuentra en L1 o L2, se busca en L3 antes de ir a la memoria principal.

¿Cómo Funciona una Caché?

El diseño de una caché implica varias decisiones importantes para que funcione de la mejor manera posible:

Dónde Guardar los Datos: Política de Ubicación

Esta política decide dónde se guardará un nuevo bloque de datos en la caché.

- Directa: Cada dato tiene un lugar fijo en la caché. Es simple, pero si dos datos diferentes necesitan el mismo lugar, la caché tiene que estar moviéndolos constantemente.

- Asociativa: Los datos pueden ir a cualquier lugar libre en la caché. Esto es más flexible, pero la computadora tiene que revisar muchos lugares para ver si el dato está allí.

- Asociativa por Conjuntos: Es una mezcla de las dos anteriores. Cada dato tiene un grupo de lugares posibles en la caché, lo que ofrece un buen equilibrio entre flexibilidad y velocidad.

Cuándo Traer Datos: Política de Extracción

Esta política decide cuándo se trae un dato de la memoria principal a la caché.

- Por Demanda: Un dato solo se trae a la caché cuando el procesador lo necesita y no lo encuentra.

- Con Prebúsqueda: Cuando el procesador pide un dato, la caché también trae los datos que están justo al lado, asumiendo que el procesador los necesitará pronto.

Qué Datos Quitar: Política de Reemplazo

Cuando la caché está llena y necesita espacio para un nuevo dato, esta política decide cuál dato antiguo debe ser eliminado.

- Aleatoria: Se elige un dato al azar para eliminar.

- FIFO (Primero en Entrar, Primero en Salir): Se elimina el dato que lleva más tiempo en la caché.

- LRU (Menos Usado Recientemente): Se elimina el dato que hace más tiempo que no se ha usado. Esta es una de las más eficientes.

- LFU (Usado con Menor Frecuencia): Se elimina el dato que se ha usado menos veces.

Cómo Actualizar Datos: Política de Escritura

Esta política decide cuándo se actualiza la información en la memoria principal cuando se cambia un dato en la caché.

- Escritura Inmediata: Los cambios se guardan al mismo tiempo en la caché y en la memoria principal para que siempre estén sincronizadas.

- Postescritura: Los cambios se guardan primero en la caché y se marcan. Solo cuando ese dato va a ser eliminado de la caché, se guardan los cambios en la memoria principal.

Mejorando el Rendimiento de la Caché

Los ingenieros siempre buscan formas de hacer que la caché funcione aún mejor. Esto se logra de varias maneras:

Tipos de Fallos en la Caché

Cuando la caché no tiene el dato que se busca, se produce un "fallo". Hay diferentes tipos de fallos:

- Forzosos: Ocurren la primera vez que se busca un dato, ya que la caché está vacía.

- Capacidad: La caché es demasiado pequeña para guardar todos los datos que el programa necesita.

- Conflicto: Diferentes datos quieren ocupar el mismo lugar en la caché, causando que se reemplacen constantemente.

Técnicas para Reducir Fallos

- Aumentar el tamaño del bloque: Traer más datos a la vez a la caché. Esto puede reducir los fallos forzosos, pero si el bloque es muy grande, puede ocupar demasiado espacio.

- Incrementar la asociatividad: Dar más opciones de dónde guardar los datos en la caché, lo que reduce los fallos por conflicto.

- Caché víctima: Añadir una pequeña caché extra para guardar los datos que acaban de ser eliminados. Si se necesitan de nuevo, se pueden recuperar rápidamente de aquí.

- Optimización del compilador: Los programas se escriben de una manera que ayuda a la caché a funcionar mejor, organizando el código para que los datos se usen de forma más eficiente.

Reducir el Tiempo de Acceso

- Cachés pequeñas y simples: Aunque tienen menos capacidad, son muy rápidas.

- Evitar la traducción de direcciones: Simplificar cómo la caché encuentra los datos para que no tenga que hacer pasos extra.

Etimología de la Palabra "Caché"

La palabra "caché" viene del inglés cache, que significa "escondite secreto". A su vez, el inglés la tomó del francés caché, que significa "escondido u oculto". Es un nombre muy apropiado para una memoria que guarda datos de forma oculta y rápida para usarlos después.

Véase también

En inglés: Cache (computing) Facts for Kids

En inglés: Cache (computing) Facts for Kids

- arquitectura de von Neumann

- caché de disco

- caché web

- unidad central de procesamiento