Biestable para niños

En electrónica, un biestable, también conocido como flip-flop o latch, es un circuito especial que tiene dos estados estables. Imagina que es como un interruptor que puede estar encendido o apagado, y se queda en ese estado hasta que le das una señal para cambiar.

Estos circuitos son muy importantes porque pueden guardar información, como un "sí" (1) o un "no" (0). Son la base de la electrónica digital y se usan en las memorias de las computadoras, en los teléfonos y en muchos otros aparatos electrónicos.

Los biestables pueden cambiar de estado cuando reciben una señal. Hay dos tipos principales según cómo reciben estas señales:

- Asíncronos: Solo tienen entradas de control. El más conocido es el biestable RS.

- Síncronos: Además de las entradas de control, tienen una entrada de "reloj" o "sincronismo". Esta entrada decide cuándo el biestable puede cambiar de estado.

La señal de reloj puede activarse de diferentes maneras: por un nivel (cuando la señal está alta o baja) o por un flanco (cuando la señal sube o baja de repente). Los biestables síncronos que se activan por flanco, llamados flip-flops, son más avanzados y resuelven algunos problemas de los biestables asíncronos.

Contenido

¿Qué es un Biestable RS?

Un biestable RS es un tipo de circuito que puede guardar un valor de 0 o 1. Tiene dos entradas principales:

- R (de Reset o Borrar): Si la activas, la salida del biestable se pone en 0 (nivel bajo).

- S (de Set o Grabar): Si la activas, la salida del biestable se pone en 1 (nivel alto).

Si no activas ninguna de las entradas (R ni S), el biestable se queda en el último estado que tenía. Es importante no activar las dos entradas (R y S) al mismo tiempo, porque esto puede causar problemas y el circuito no sabría qué hacer.

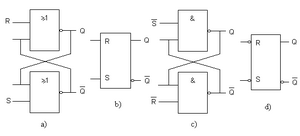

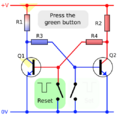

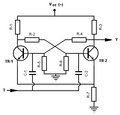

Biestable RS Asíncrono

Este tipo de biestable RS solo tiene las entradas R y S. Se construye usando compuertas lógicas llamadas NAND o NOR.

Aquí te mostramos cómo funciona con una tabla:

| R | S | Salida (NOR) | Salida (NAND) | ||||

|---|---|---|---|---|---|---|---|

|

|

|

|

|

||||

|

|

|

|

|

||||

|

|

|

|

|

||||

|

|

|

|

|

||||

| "No deseado" significa que no se debe usar esa combinación. "Se mantiene" significa que el estado no cambia. | |||||||

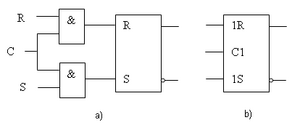

Biestable RS Síncrono

Este biestable RS tiene una entrada adicional llamada C (de "Clock" o reloj). Esta entrada C decide cuándo las señales R y S pueden afectar al biestable. Si C está en 0, el biestable no cambia de estado, sin importar lo que hagan R y S.

Su tabla de verdad es la siguiente:

| C | R | S | Salida (NOR) |

|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| X = no importa (el valor no afecta el resultado) | |||

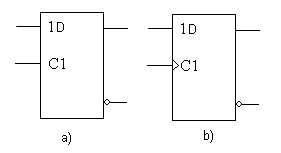

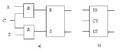

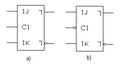

¿Qué es un Biestable D?

El biestable D (de "Data" o Datos) es muy útil para guardar un solo bit de información. Su salida (Q) simplemente copia lo que hay en su entrada D cuando la señal de reloj se activa. Es como un pequeño "retardo" de un ciclo de reloj.

Su tabla de verdad es sencilla:

| D | Salida actual | Próxima Salida |

|---|---|---|

| 0 | X |

|

| 1 | X |

|

| X = no importa | ||

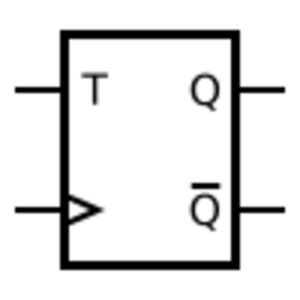

¿Qué es un Biestable T?

El biestable T (de "Toggle" o alternar) cambia su estado cada vez que la señal de reloj se activa, siempre y cuando su entrada T esté en nivel alto. Si la entrada T está en nivel bajo, el biestable mantiene su estado anterior.

Su tabla de verdad muestra cómo alterna:

| T | Salida actual | Próxima Salida |

|---|---|---|

| 0 | 0 |

|

| 0 | 1 |

|

| 1 | 0 |

|

| 1 | 1 |

|

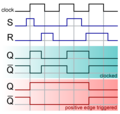

¿Qué es un Biestable JK?

El biestable JK es muy versátil y uno de los más usados. Funciona de manera similar al biestable RS, pero tiene una ventaja importante: no tiene la "condición no deseada" que ocurre cuando las dos entradas se activan al mismo tiempo.

Tiene dos entradas principales, J y K:

- J: Si la activas, la salida se pone en 1.

- K: Si la activas, la salida se pone en 0.

Si J y K están en 0, el biestable mantiene su estado. La gran diferencia es que si J y K están en 1 al mismo tiempo, la salida cambia al estado contrario al que tenía.

Su tabla de verdad es:

| J | K | Próxima Salida |

|---|---|---|

| 0 | 0 | Se mantiene |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | Cambia al contrario |

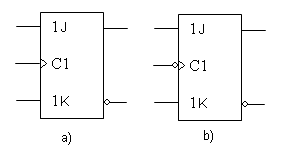

Biestable JK Activo por Flanco

Este biestable JK tiene una entrada de reloj (C) que permite que el cambio de estado ocurra solo cuando la señal de reloj sube o baja (un flanco).

Cuando J y K están en 1, cada vez que llega un flanco activo en la señal de reloj, la salida del biestable cambia de estado. A esto se le llama modo de "basculación" o toggle.

¿Para qué se usan los Biestables?

Los biestables son fundamentales en la electrónica digital. Aquí te explicamos algunos de sus usos:

Almacenar Información

Un biestable puede guardar un solo bit de información (un 0 o un 1). Si juntas muchos biestables, puedes almacenar datos más grandes, como números, letras o el estado de un programa en una computadora.

Contadores

Los biestables T son muy útiles para contar. Si conectas varios biestables T en cadena, cada uno dividirá la frecuencia de la señal de entrada por dos. Al final, la cadena de biestables puede contar en código binario cuántos ciclos de reloj han pasado.

Máquinas de Estado

Los biestables se usan para construir "máquinas de estado finitas". Estas máquinas son como cerebros simples que recuerdan lo que pasó antes para decidir qué hacer después. Por ejemplo, un semáforo usa una máquina de estado para saber en qué color está y cuándo cambiar al siguiente.

Problemas con los Biestables: Metaestabilidad

A veces, los biestables síncronos pueden tener un problema llamado metaestabilidad. Esto ocurre si una señal de entrada cambia justo en el momento exacto en que llega la señal de reloj. Es como si el biestable no supiera si la señal llegó antes o después del reloj.

Cuando esto pasa, la salida del biestable puede tardar más de lo normal en decidirse, o incluso puede oscilar un poco antes de estabilizarse. En una computadora, esto podría causar errores en los datos.

Los ingenieros diseñan los circuitos para evitar la metaestabilidad, asegurándose de que las señales de entrada estén estables un tiempo antes y después de la señal de reloj. Aunque es muy difícil eliminar este problema por completo, se pueden usar técnicas para reducir mucho la probabilidad de que ocurra.

Galería de imágenes

Véase también

En inglés: Flip-flop (electronics) Facts for Kids

En inglés: Flip-flop (electronics) Facts for Kids