Acceso directo a memoria para niños

El acceso directo a memoria (DMA, por sus siglas en inglés direct memory access) es una función muy útil en las computadoras. Permite que algunos componentes de tu equipo, como las tarjetas gráficas o los discos duros, accedan directamente a la memoria principal para guardar o leer información. Lo hacen sin necesidad de que la unidad central de procesamiento (CPU), que es como el "cerebro" de la computadora, los supervise todo el tiempo.

El DMA es fundamental en todas las computadoras modernas. Imagina que la CPU es un director de orquesta muy ocupado. Si cada instrumento (componente) tuviera que pedirle permiso para tocar (acceder a la memoria), el director se agotaría. Con DMA, algunos instrumentos pueden tocar solos, liberando al director para otras tareas importantes. Esto hace que la computadora funcione mucho más rápido y de manera más eficiente, especialmente cuando se mueven grandes cantidades de datos.

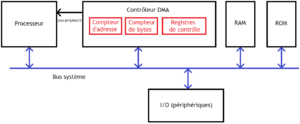

Una transferencia DMA es como copiar un gran bloque de información de un lugar a otro. Por ejemplo, de un disco duro a la memoria RAM. En lugar de que la CPU haga esta copia paso a paso, un controlador especial de DMA se encarga de ello. Así, la CPU queda libre para hacer otras cosas, lo que mejora el rendimiento de los programas que necesitan muchos recursos.

Aunque la CPU no participa directamente en la transferencia de datos, el DMA sí necesita usar los "caminos" internos de la computadora, llamados buses. Por eso, existen diferentes formas de organizar el uso de estos caminos para que el DMA no los ocupe por completo y la CPU también pueda usarlos.

Contenido

¿Cómo el DMA afecta la memoria caché del procesador?

El DMA puede generar un pequeño desafío llamado problema de coherencia en la memoria caché del procesador. La memoria caché es una memoria muy rápida y pequeña que la CPU usa para guardar copias de los datos que usa con frecuencia. Así, no tiene que ir a la memoria principal cada vez.

Imagina que la CPU tiene una copia de un dato "X" en su caché. Si un dispositivo usa DMA para cambiar el dato "X" en la memoria principal, la CPU podría seguir usando la copia antigua que tiene en su caché. Esto haría que la CPU trabaje con información desactualizada.

Para evitar esto, hay dos soluciones principales:

- Sistemas con caché coherente: Estos sistemas tienen un diseño especial que permite que el hardware se comunique con la caché. Si el DMA escribe un dato en la memoria principal, la caché se "entera" y actualiza o invalida su copia. Si el DMA va a leer un dato, la caché se asegura de que la versión más reciente esté en la memoria principal.

- Sistemas no coherentes: En estos sistemas, el sistema operativo (el programa principal de la computadora) es el encargado de asegurarse de que la caché esté al día. Antes de que el DMA lea o escriba, el sistema operativo le dice a la CPU que guarde los datos de la caché en la memoria principal o que descarte las copias antiguas. Esto requiere un poco más de trabajo del sistema operativo, pero asegura que la información sea correcta.

También existen sistemas híbridos que combinan ambas soluciones para un mejor rendimiento.

¿Cómo funciona una operación de DMA?

Una operación de DMA sigue una serie de pasos para mover datos. Piensa en ello como una entrega de paquetes muy organizada:

Pasos básicos de una transferencia DMA

1. Preparación: La CPU le dice al controlador de DMA dónde están los datos que se van a mover (la dirección de memoria) y cuántos datos son. 2. Solicitud: El dispositivo que necesita mover datos (como un disco duro) le pide al controlador de DMA que inicie la transferencia. 3. Control del bus: El controlador de DMA le pide a la CPU permiso para usar los caminos de datos (el bus del sistema). La CPU le da el permiso. 4. Transferencia: El controlador de DMA toma el control del bus y empieza a mover los datos directamente entre el dispositivo y la memoria. Por cada dato que se mueve, el controlador actualiza la cuenta de datos restantes y la dirección de memoria. 5. Finalización: Cuando todos los datos se han movido, el controlador de DMA le avisa a la CPU que la tarea ha terminado.

Tipos de transferencias DMA

El rendimiento de la computadora puede verse afectado cuando el DMA usa mucho el bus, ya que la CPU podría tener que esperar para acceder a la memoria. Para manejar esto, existen dos formas principales en que el DMA realiza las transferencias:

- Transferencias en modo ráfaga: Una vez que la CPU le da permiso al DMA para usar el bus, el DMA lo mantiene ocupado hasta que termina de mover todos los datos. Este modo es eficiente si la CPU tiene su propia memoria caché, porque puede seguir trabajando con los datos que ya tiene guardados allí mientras el DMA está ocupado.

- Transferencias en modo robo de ciclo: En este modo, el DMA toma el bus, transfiere una pequeña cantidad de datos (una "palabra"), y luego lo libera. Después, vuelve a pedir permiso para transferir la siguiente parte. Este proceso se repite hasta que todos los datos se han movido. Aunque la transferencia total tarda más, permite que la CPU siga ejecutando instrucciones entre cada "robo" de ciclo, lo que es útil en sistemas sin mucha memoria caché.

Ejemplos de uso de DMA en computadoras

El DMA se ha implementado de diferentes maneras a lo largo de la historia de las computadoras:

DMA en arquitecturas antiguas (ISA)

En computadoras más antiguas, como las que usaban la arquitectura ISA, había un controlador de DMA centralizado. Este controlador tenía varios "canales" para que diferentes dispositivos pudieran usar el DMA. Por ejemplo, el controlador de disquetes o algunos discos duros usaban estos canales. Con el tiempo, estos sistemas fueron mejorando, pero su velocidad era limitada.

DMA en arquitecturas modernas (PCI)

Las computadoras modernas con arquitectura PCI no tienen un controlador de DMA central como las antiguas. En su lugar, cualquier componente PCI puede pedir el control del bus y acceder directamente a la memoria. Es como si cada dispositivo pudiera ser su propio "maestro" del bus. Si varios dispositivos quieren ser maestros al mismo tiempo, hay un sistema que decide quién lo usa primero.

Esto permite transferencias de datos mucho más rápidas. Sin embargo, a veces, si un procesador usa mucha memoria (más de 4 GB), los dispositivos DMA más antiguos podrían tener problemas para acceder a direcciones de memoria muy altas. Para solucionar esto, se usan tecnologías especiales o el sistema operativo ayuda a gestionar las direcciones.

DMA en sistemas integrados (AHB)

En dispositivos más pequeños y especializados, como los que se encuentran en teléfonos o sistemas embebidos, se usan buses como el AMBA AHB. Aquí, los dispositivos pueden tener una interfaz "maestra" para hacer transferencias DMA rápidas a la memoria del sistema, sin ralentizar el procesador principal. Esto es muy útil para componentes que manejan muchos datos, como los controladores de red.

Mejoras de DMA en procesadores avanzados

Algunos procesadores modernos, como los Intel Xeon, incluyen tecnologías de DMA avanzadas directamente en sus chips. Un ejemplo es la I/O Acceleration Technology (I/OAT), diseñada para mejorar el rendimiento de las redes de alta velocidad. Aunque estas mejoras son sutiles, contribuyen a que las computadoras sean más eficientes en tareas que requieren mucho movimiento de datos.

|

Véase también

En inglés: Direct memory access Facts for Kids

En inglés: Direct memory access Facts for Kids