Coherencia de caché para niños

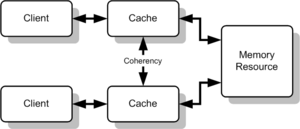

La coherencia de caché se refiere a que los datos guardados en las memorias caché de un sistema sean siempre correctos y estén actualizados. Imagina que varios usuarios o partes de un ordenador comparten la misma información. La coherencia de caché asegura que todos vean la versión más reciente de esa información. Es un tipo especial de coherencia de memoria.

Cuando diferentes partes de un ordenador, como los procesadores en un sistema con varios de ellos, guardan copias de la misma información en sus propias memorias caché, pueden surgir problemas. Por ejemplo, si un procesador tiene una copia de un dato y otro procesador cambia ese dato, el primer procesador podría estar usando una versión antigua sin saberlo. La coherencia de caché ayuda a evitar estos problemas, manteniendo la información igual en todas las cachés y en la memoria principal.

Contenido

¿Cómo se mantiene la coherencia de caché?

Existen diferentes métodos para asegurar que la información en las cachés esté siempre coordinada. Estos métodos se llaman protocolos.

Protocolos basados en directorio

Estos protocolos usan un "directorio" central. Este directorio es como una lista que sabe qué partes de la memoria están guardadas en cada caché. Así, cuando un dato cambia, el directorio solo avisa a las cachés que tienen una copia de ese dato. Esto ayuda a que el sistema no envíe demasiados mensajes y funcione más rápido. Se usan en ordenadores con muchos procesadores y memoria distribuida.

Protocolo Snoopy

En este método, cada caché "espía" o "escucha" lo que pasa en el bus de datos (como una autopista por donde viaja la información). Si una caché ve que un dato que ella tiene guardado es modificado por otra parte del sistema, automáticamente invalida su copia. Esto significa que la marca como "no válida" y sabe que necesita obtener la versión más reciente. También puede intentar actualizar su copia directamente si ve el nuevo dato.

Protocolo de memoria distribuida

Este protocolo es similar a los anteriores, pero se usa en sistemas donde las partes del ordenador no están tan conectadas directamente. Su objetivo es mantener la información consistente entre diferentes bloques de memoria.

Modelos de coherencia: ¿Qué opciones existen?

Se han creado varios modelos y protocolos para mantener la coherencia de caché. Algunos de los más conocidos son:

- Protocolo MSI

- Protocolo MESI

- Protocolo MOSI

- Protocolo MOESI

Elegir el modelo adecuado es muy importante al diseñar un sistema de caché. Cada modelo tiene sus propias ventajas en cuanto a velocidad y capacidad de crecimiento. Por eso, los ingenieros evalúan cuál es el mejor para cada tipo de ordenador.

Además, la forma en que estos protocolos cambian el estado de los datos puede variar. Por ejemplo, algunos pueden actualizar la información al leerla, mientras que otros la invalidan al escribir. Estas decisiones afectan la cantidad de información que se mueve entre las cachés. Esto es importante para que el sistema funcione de manera eficiente y no se ralentice.

Véase también

En inglés: Cache coherence Facts for Kids

En inglés: Cache coherence Facts for Kids

- Bus sniffing

- Protocolos de coherencia basados en directorio

- NUMA

- Write barrier